設計例 その3

4ビットCPUの設計 その3

ここでは,8ビットCPUのK-COMを元に,4ビットCPU設計を行う.命令長は8ビットのままとし,図1に示すように4ビットのデータを命令レジスタに2回に分けて読み込むことにする. 機械語の構成は8ビットK-COMと同じである.4ビット版K-COMの全体の構成を図2に示す.

図1 4ビットCPUの命令構成

図2 4ビットCPUの構成

命令の読み出し方法が変わったため,フェッチおよび実行サイクルは図3に示すように変更した.

図3 コントローラの動作

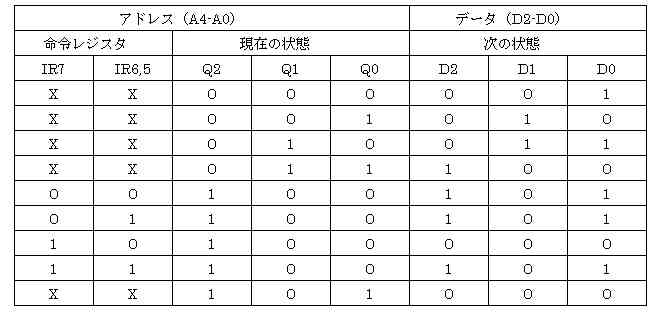

この場合,コントローラの回路も変更が必要となる.全部でS0からS5までの6サイクルあるので,3ビットの記憶素子が必要となる.K-COMの状態遷移回路はPROMとD-FFにより作成されていたが,PROMのアドレスは5ビットしかなく,命令コード3ビットと記憶素子3ビットを入力することはできない.そこで,命令コードの冗長性から2ビットにエンコードして状態遷移ROMの設計を行った.具体的には,命令の種類によって実行サイクルが1サイクルと2サイクルに分岐する部分のみの検出を行えばよい.IR7が0なら演算命令で実行サイクルは2サイクル,IR7が1でIR6の否定とIR5のANDが1の時にST命令実行で2サイクル,それ以外では1サイクルとなる.以上から状態遷移ROMの真理値表を表1のように設計した.

表1 状態遷移ROMの設計

そのほか,制御信号にも若干の変更がある.命令レジスタを2回に分けて読み込む際,2個のレジスタを4ビットずつ用い,それぞれのCE信号を制御したが,制御信号出力用のROMのデータバスにも余りがない.そこで,K-COMの命令レジスタのCE制御信号と状態遷移回路のD-FFの出力を組み合わせて2個のレジスタをそれぞれ制御するようにした.

フェッチサイクル制御用ROMの回路も変更した.フェッチにはS0からS3までの4サイクルの出力が必要なため,ROMのアドレス信号を変更し,アドレス0,1,2,3までを有効とし,8ビット版K-COMのS0,S1,S0,S1状態の制御信号を順に出力するようにROMデータを追加した.

以上の変更を加えて作成した4ビットCPUの全回路は図4である.

図4 4ビットCPUの全回路

CircuitMaker用回路データのダウンロード

ジャンル別一覧

人気のクチコミテーマ

-

-

- デジタル一眼レフカメラ

- 今ならまだ買える!Nikon 一眼レフカ…

- (2024-11-10 10:56:12)

-

-

-

- パソコンサポーターがすすめるパソコ…

- ◎新品 デスクトップパソコン HP 液晶…

- (2024-10-04 11:38:18)

-

-

-

- パソコンを楽しむ♪

- PC用オーディオラックの棚増設

- (2024-11-20 23:27:15)

-

© Rakuten Group, Inc.